首先为什么要定点化?

在性能可接受的范围内尽可能的的压缩数据bit位宽以便节省资源

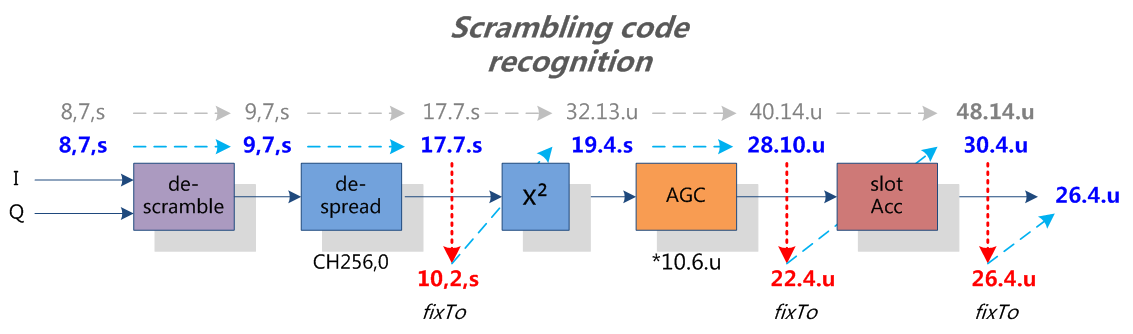

一个扰码识别的定点流程

灰色的全精度

蓝色是定点截位以后的位宽,对于这个算法,定点以后在大大节省资源的情况下性能几乎没有任何损失。

我们在定点的时候不是说每一个节点都需要压缩bit,而是在关键的节点尽可能压缩位宽才能做到事半功倍,

比如以上例子中的求平方,和最后的累计和输出,这两个点对硬件来说非常敏感,一个是乘法器,另外一个是缓存MEM,是面积的开销大户,

所以我们在定点的时候要特别有意去照顾这些节点,在性能可接受的情况下,能省1bit是1bit

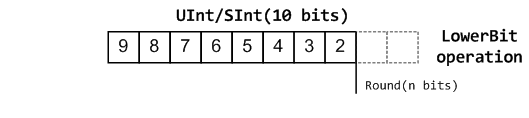

定点介绍(低截高饱)

一般我们会分为两步来操作

- 低位Round操作

低位的Round操作有非常多类型。参见

https://en.wikipedia.org/wiki/Rounding