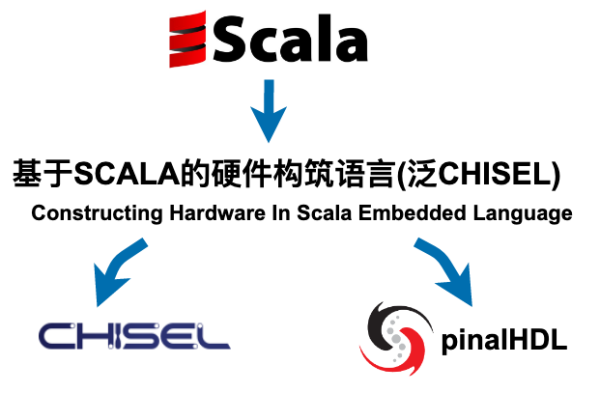

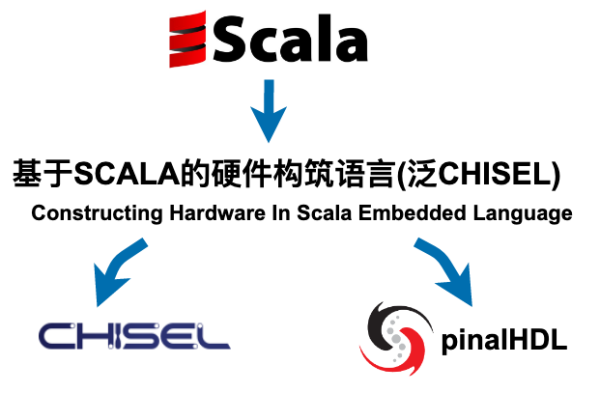

这里有两个概念

基于Scala的硬件构筑语言(Constructing Hardware In Scala Embedded

Language)

包括chisel和SpinalHDL, 所以标题中为什么需要CHISEL是指为什么需要一个基于Scala的HDL语言,实际上chisel和SpinalHDL称为HDL框架更为合适,因为除了一些电路语法外,绝大多数都是在运用Scala的语言功能,一切强大都源于Scala语法。

伯克利大学发布的Chisel硬件开发语言

我们文章中大CHISEL为泛指, 小Chisel为特指。

Verilog不够用吗?

需要一门新的语言吗?

VHDL诞生于1982年 ,Verilog诞生于1981年, 起初是用来电路存档描述,

都是硬件描述语言, 是用来描述数字电路的结构,行为,功能和接口的语言。

虽然Verilog/VHDL简单易用,在一定的历史时期确实是一个效率的巨大提升,

但是目前来看,槽点依然很多,

已经有点落伍时代。即便是SystermVerilog一定程度上改善了它 存在的问题,

并没有完全解决Verilog的问题,况且EDA工具对SV的支持并不是很积极,所以依然是尴尬的存在。

例化不方便

有人会说,有辅助插件帮你完成 (确实有很多好的插件,emacs verilog-mode

, vim 的autoinst) 即便这样,但是对带参数的模块例化,

一对多例化同样需要手动处理,非常不方便

大量的重复声明

无休止的变量声明,无休止的位宽声明,容易出错,

作为一门上古时期的语言,对编译器不能要求太高

函数不能带参数

verilog中函数的使用只能是零零星星,哪怕是一个位宽的变化都要重写函数,

作为一门语言函数不能广泛使用,实为鸡肋

参数化实在是笨拙

虽然支持参数化,parameter 也只能做一些简单的加减左移操作,

没有基本math包。

利用宏做参数化,对于变量比较多的设计,非常复杂,并且也不好维护

目前我也看到

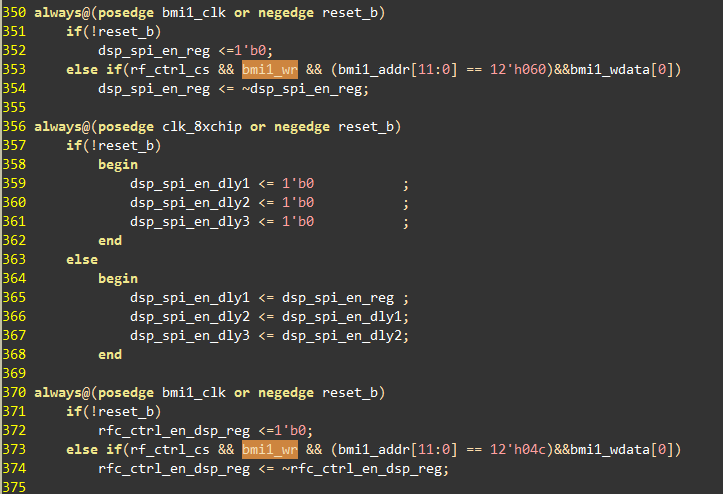

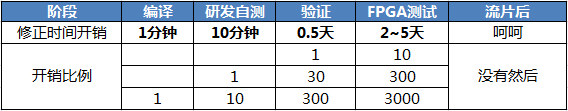

错误检测很弱

编译工具对错误的处理比较保守,

这种保守可能也源于语言本身,以及编译器的能力不及。

- 位宽不匹配,

- input/output端口写反

- 饱和截位弄错,

- 跨时钟域问题

- 锁存器检查

- 组合逻辑环自己查

- ….

基于前仿的编译,还会遗漏大量的错误,必须要Lint, 综合检查,

费时费力又费钱。

重构、增减信号,Bist/DFT逻辑插入麻烦

需要手动插入, 编写脚本, 即便是脚本也不通用

等等…